LAB AND SENSOR EQUIPMENT

Lab measurements fail most often on repeatability: small timing differences create different results. FPGA-based acquisition makes timing and triggers consistent, so measurements behave the same run after run.

• Channels stay aligned with consistent timestamps across inputs

• Triggers become repeatable using hardware windowing and event capture

• Data integrity is visible via counters and checks during streaming

Typical Use Cases in Lab & Sensor Equipment

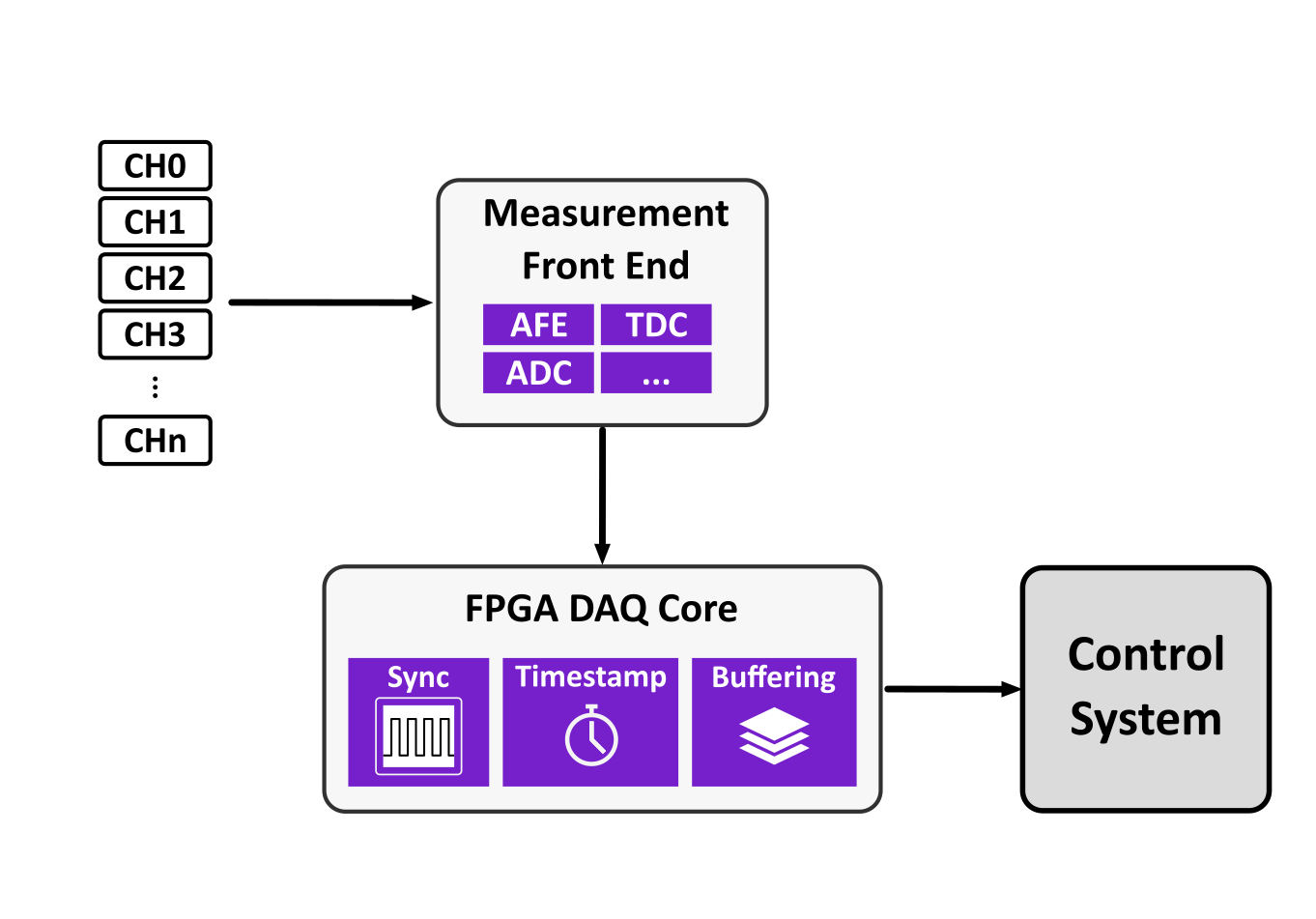

Modular Multi-Channel DAQ Platforms for Laboratories and Test Facilities

Lab DAQ systems often fail on repeatability: channel alignment drifts, trigger timing is ambiguous, and sustained streaming breaks under real workloads. FPGA-based acquisition provides tightly synchronized multi-channel sampling with deterministic timestamps and a stable data path at sustained rates. This improves comparability across experiments and enables reliable pre/post-event capture when transients matter. Where needed, the complete measurement front-end—sensor interface, analog conditioning and clocking/synchronization—is developed as an integrated subsystem.

Deterministic Triggering and Event-Timed Acquisition for Fast Phenomena

Many experiments depend on precise time reference and repeatable event capture: triggers, gates, windows and latency must be known and constant. FPGA-based pipelines implement fixed-latency triggering, windowing and event processing independent of software timing, enabling reproducible measurements across runs. This is useful for fast transients and pulse-like signals where timing errors directly degrade results. The emphasis is on measurable, verifiable timing behavior rather than “best effort” real-time software.

High-Rate Instrumentation Front-Ends for Photonics and Specialized Sensors

Photonics and specialized detectors often combine unusual interfaces with high bandwidth and strict timing: sensor readout, framing and synchronization become the integration risk. FPGA-based front-ends implement timing-accurate interfaces (ADC/DAC/TDC paths), deterministic alignment and robust buffering/streaming to the host. This provides a predictable foundation for analysis software while keeping the acquisition behavior stable and observable. The scope focuses on acquisition integrity and timing; higher-level analysis remains on the host platform.

Sensor Development and Verification Test Setups

When developing or evaluating sensors, controlled and repeatable stimuli and measurement conditions are essential: timing, synchronization and corner cases must be reproducible. FPGA-based test setups provide deterministic signal generation, precise timing control and integrated acquisition paths for characterization and comparative tests. This reduces dependence on fragile software timing and makes test results easier to reproduce across teams and sites. The result is a stable platform for validation, calibration and long-term regression measurements.