INDUSTRIAL APPLICATIONS

Industrial signals are messy: spikes, drift and timing gaps hide the real condition of a machine. FPGA-based acquisition keeps channels aligned and captures relevant events at the source.

• Signals stay aligned across vibration/pressure/flow channels

• Short events get captured instead of being averaged away

• Hardware reactions stay predictable when faults occur

Typical Use Cases in Industrial Systems

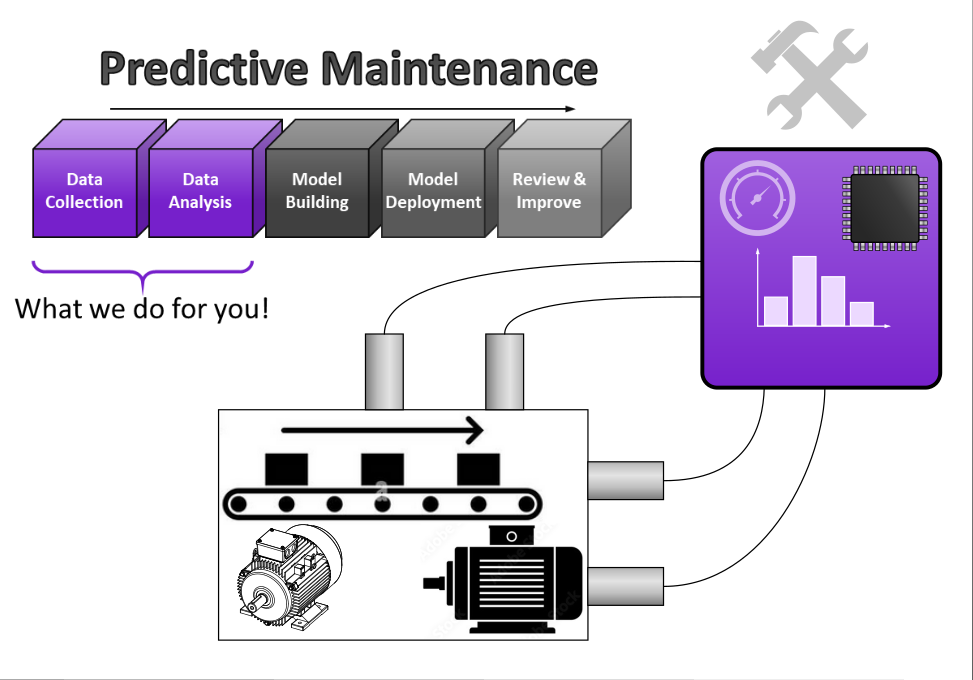

Condition Monitoring for Machines and Process Equipment

Condition-monitoring products often fail on timing and data integrity: channels drift, transient events are missed and preprocessing happens too late. FPGA-based acquisition enables tightly synchronized multi-sensor sampling (vibration/pressure/flow), deterministic timestamping and real-time event capture close to the source. This improves repeatability of indicators and reduces data volume before the PLC/edge system. Where needed, sensor selection and front-end design can be developed as part of the solution.

Safety Interlocks and Protection Paths in Industrial Control

Safety functions implemented purely in software can become sensitive to load, scheduling and update side effects. FPGA-based protection logic provides an independent, deterministic layer for interlocks, limit checks, watchdogs and fault latching, with defined safe states on reset and power events. This separation reduces common-mode failures and makes fault behavior measurable and reproducible during commissioning.

Commissioning and Regression Testing via HIL Sensor Emulation

Commissioning effort increases when faults are hard to reproduce and test runs vary in timing. FPGA-based HIL setups provide deterministic I/O behavior with precise update rates, enabling repeatable scenarios, controlled edge cases and automated regression tests for PLC/drive/control logic. This reduces on-site debugging time and supports long-term maintenance by making behavior verifiable after changes.

Industrial Vision Interfaces for Inspection and Automation

In industrial vision products, the main risk is often reliable transport and timing alignment rather than the vision algorithm itself. FPGA-based interface logic can stabilize camera readout timing, frame synchronization and trigger/strobe alignment, and implement buffering/monitoring to protect the host from data-rate spikes. The scope typically focuses on interfacing and deterministic streaming; higher-level image processing remains on the host.