MEDICAL APPLICATIONS

When devices rely on sensor data, timing should remain stable across operating modes and software load. FPGA-based data paths keep sampling and processing consistent and easier to validate.

• Sampling stays consistent across multiple channels

• Latency stays predictable from input to output

• System behavior stays defined with optional supervision logic

Typical Use Cases in Medical Devices

Multi-Channel Bio-Signal Front-Ends for Medical Devices and Wearables

Fixed-Latency Conditioning for Diagnostics and Control

High-Throughput Sensor Interfaces for Imaging-Based Devices

Hardware Supervision and Defined Safe-State Behavior

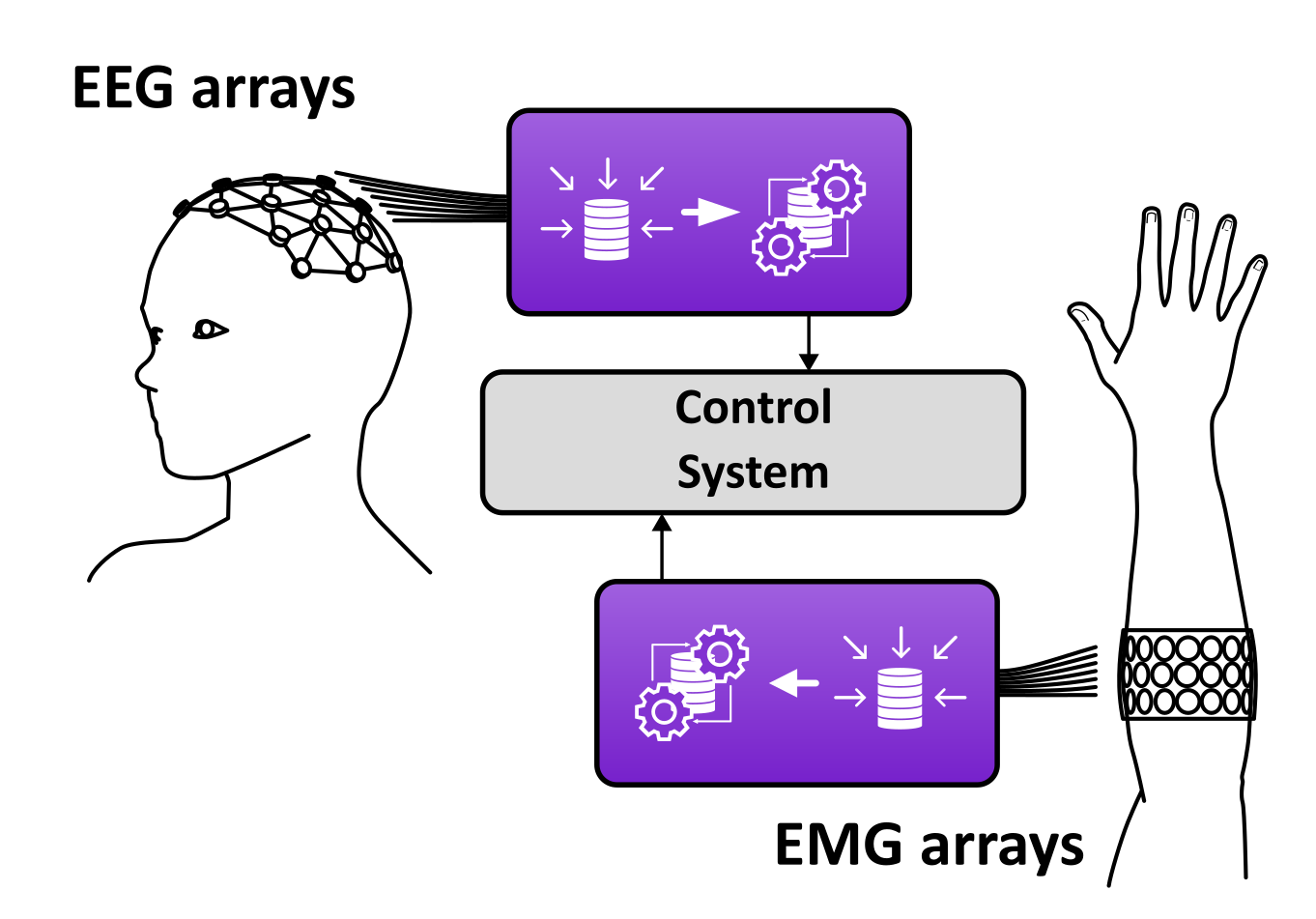

Multi-Channel Bio-Signal Front-Ends for Medical Devices and Wearables

Multi-sensor bio-signal products often struggle with timing integrity: channels are not perfectly aligned, latency varies with system load and artifacts are harder to separate when sampling is inconsistent. FPGA-based front-ends enable deterministic multi-channel acquisition with tight synchronization and precise timestamping close to the electrodes/sensors. This stabilizes downstream processing and improves repeatability across devices and operating modes. Where needed, the complete front-end (sensor selection, analog conditioning, ADC architecture and synchronization concept) can be developed as an integrated subsystem.

Fixed-Latency Conditioning for Diagnostics and Control

In diagnostics and assistive systems, the value often depends on reproducible timing: filters, gating, triggering and feature extraction should behave identically across runs and system states. FPGA-based pipelines provide fixed-latency signal conditioning and event detection independent of CPU scheduling, enabling consistent measurements and reliable real-time behavior. This can reduce host processing load and data bandwidth while keeping the signal chain verifiable. The processing scope is typically focused on timing-critical stages; higher-level analytics remain on the main compute platform.

High-Throughput Sensor Interfaces for Imaging-Based Devices

Imaging-oriented medical products are frequently limited by data movement and deterministic capture rather than compute: stable sensor readout, framing and sustained streaming determine whether the pipeline remains reliable. FPGA-based interfaces implement timing-accurate readout, synchronization to triggers and robust buffering/monitoring to protect the host from data-rate spikes. This provides a predictable foundation for host-side processing and shortens integration risk when sensor links and timing are non-trivial. The emphasis is on deterministic acquisition and transport, not on claiming full image-processing IP.

Hardware Supervision and Defined Safe-State Behavior

Systems that interact with humans benefit from an independent, deterministic supervision layer: limit violations, plausibility faults and loss-of-control conditions should lead to defined states that do not depend on OS behavior or main CPU load. FPGA-based supervision implements watchdogs, interlocks, limit checks and inhibit paths with well-defined reset and power-up behavior. This separation reduces common-mode failures between application software and protective reactions and makes fault handling measurable during verification. The result is clearer system behavior under fault conditions and simpler integration of safety-relevant functions.